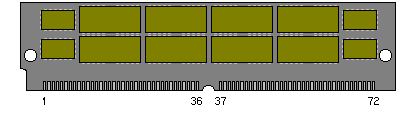

72 pin ECC SIMM

From HwB

SIMM=Single Inline Memory Module

ECC=Error Correcting Code

Pinout

72 PIN SIMM at the computer.

| Pin | ECC | Optimized | Description |

|---|---|---|---|

| 1 | VSS | VSS | Ground |

| 2 | DQ0 | DQ0 | Data 0 |

| 3 | DQ1 | DQ1 | Data 1 |

| 4 | DQ2 | DQ2 | Data 2 |

| 5 | DQ3 | DQ3 | Data 3 |

| 6 | DQ4 | DQ4 | Data 4 |

| 7 | DQ5 | DQ5 | Data 5 |

| 8 | DQ6 | DQ6 | Data 6 |

| 9 | DQ7 | DQ7 | Data 7 |

| 10 | VCC | VCC | +5 VDC |

| 11 | PD5 | PD5 | Presence Detect 5 |

| 12 | A0 | A0 | Address 0 |

| 13 | A1 | A1 | Address 1 |

| 14 | A2 | A2 | Address 2 |

| 15 | A3 | A3 | Address 3 |

| 16 | A4 | A4 | Address 4 |

| 17 | A5 | A5 | Address 5 |

| 18 | A6 | A6 | Address 6 |

| 19 | n/c | n/c | Not connected |

| 20 | DQ8 | DQ8 | Data 8 |

| 21 | DQ9 | DQ9 | Data 9 |

| 22 | DQ10 | DQ10 | Data 10 |

| 23 | DQ11 | DQ11 | Data 11 |

| 24 | DQ12 | DQ12 | Data 12 |

| 25 | DQ13 | DQ13 | Data 13 |

| 26 | DQ14 | DQ14 | Data 14 |

| 27 | DQ15 | DQ15 | Data 15 |

| 28 | A7 | A7 | Address 7 |

| 29 | DQ16 | DQ16 | Data 16 |

| 30 | VCC | VCC | +5 VDC |

| 31 | A8 | A8 | Address 8 |

| 32 | A9 | A9 | Address 9 |

| 33 | n/c | n/c | Not connected |

| 34 | /RAS1 | /RAS1 | Row Address Strobe 1 |

| 35 | DQ17 | DQ17 | Data 17 |

| 36 | DQ18 | DQ18 | Data 18 |

| 37 | DQ19 | DQ19 | Data 19 |

| 38 | DQ20 | DQ20 | Data 20 |

| 39 | VSS | VSS | Ground |

| 40 | /CAS0 | /CAS0 | Column Address Strobe 0 |

| 41 | A10 | A10 | Address 10 |

| 42 | A11 | A11 | Address 11 |

| 43 | /CAS1 | /CAS1 | Column Address Strobe 1 |

| 44 | /RAS0 | /RAS0 | Row Address Strobe 0 |

| 45 | /RAS1 | /RAS1 | Row Address Strobe 1 |

| 46 | DQ21 | DQ21 | Data 21 |

| 47 | /WE | /WE | Read/Write |

| 48 | /ECC | /ECC | |

| 49 | DQ22 | DQ22 | Data 22 |

| 50 | DQ23 | DQ23 | Data 23 |

| 51 | DQ24 | DQ24 | Data 24 |

| 52 | DQ25 | DQ25 | Data 25 |

| 53 | DQ26 | DQ26 | Data 26 |

| 54 | DQ27 | DQ27 | Data 27 |

| 55 | DQ28 | DQ28 | Data 28 |

| 56 | DQ29 | DQ29 | Data 29 |

| 57 | DQ30 | DQ30 | Data 30 |

| 58 | DQ31 | DQ31 | Data 31 |

| 59 | VCC | VCC | +5 VDC |

| 60 | DQ32 | DQ32 | Data 32 |

| 61 | DQ33 | DQ33 | Data 33 |

| 62 | DQ34 | DQ34 | Data 34 |

| 63 | DQ35 | DQ35 | Data 35 |

| 64 | n/c | DQ36 | Data 36 |

| 65 | n/c | DQ37 | Data 37 |

| 66 | n/c | DQ38 | Data 38 |

| 67 | PD1 | PD1 | Presence Detect 1 |

| 68 | PD2 | PD2 | Presence Detect 2 |

| 69 | PD3 | PD3 | Presence Detect 3 |

| 70 | PD4 | PD4 | Presence Detect 4 |

| 71 | n/c | DQ39 | Data 39 |

| 72 | VSS | VSS | Ground |

Contributions

Sources

- Various productsheets at IBM Memory Products